PCIe DMA System

Uses of Intel Cyclone IV PCIe with DMA under Ms-Windows and Linux

PCIe 2xSGDMA

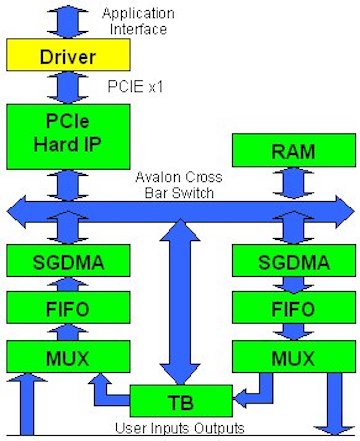

Dual SGDMA-SYS PCI Express Dual SGDMA system

The present basic system is targeted for extreme DMA Application. It includes a system with 2 SGDMA channels whose block diagram can be seen in the right picture.

The two SGDMA channels are configured one in input and one in output. Customer’s logics can be connected to user Inputs/Outputs pins. The mux, under control of an Avalon’s register, can route the DMA channels ST interface from the I/O pins to TB module. The TB Pheripheral can be used to test the system and measure its performance. The TB peripheral contains a timer, a loopback, a speed programmable pattern checker and/or generator. The test mode of TB block can be programmed from Avalon bus. The fifos inside the input output data path allow to mantain the data transfer rate during DMA descriptor and TLB handling in large DMA. A simple test programm, using the TB block, tests and measures the performance in different driver layouts.

The interface (ST) inside MUX-FIFO-SGDMA chain and inside SGDMA-PCIe Hard IP are designed to obtain the maximum reacheable performance.

- Click here to open data sheet

- Click here to view all documents list

Buy Online

- 120107-02A1 MS-Windows 32bits, XP and Seven version

- 120107-02A3 MS-Windows 64bits, Seven version

- 120107-02A4 Linux64 version