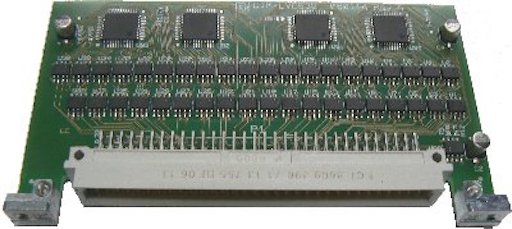

BSPIO-LVDS39

Digital Modules for Boundary Scan I/O Access

JTAG LVDS I/O parallel module

Features:

- 39 LVDS I/O channels for interface logic drive and sense

- High reliability DIN41612 I/O connector

- Reliable screw lock brackets

- Size 122mm X 70mm

- 96 bit Boundary-scan Register Length

- Each segment can be independently bypassed

- Medium-speed 10MHz TCK for high reliability at the best cost/performance ratio

- Each LVDS I/O pin is independently programmable for sense, drive, bi-directional, and tri-state operation

- Fully-compatible JTAG/IEEE 1149.1 Test Access Port (TAP)

- Optional LVDS TCK interface can be used in large fixtures to avoid noise and skew problems.

- Full self test capability using internal loopback.

General Description

The BSPIO-LVDS39 provides bi-directional parallel-scan access to up to 39 electrical nodes with LVDS interfaces for the driving and sensing of logic values. This module increases the effectiveness of boundary-scan testing, enabling verification of all board connectors and within logic clusters. The BSPIO-LVDS39 is available in two basic versions, both of them compatible with the standard DIN41612 female connectors in a test fixture. One version, the BSPIO-LVDS39-A1, is primarily intended for test fixtures with few BSPIOsand contains a standard TTL interface on the TAP’s TCK signal. This module facilitates boundary-scan interconnection testing using direct connection to the JTAG/IEEE 1149.1 Test Access Port (TAP).

The other version, the BSPIO-LVDS39-A2, is intended for test fixtures with many BSPIOs and contains a balanced LVDS interface on the TAP’s TCK signal. This module facilitates boundary-scan interconnection testing using a small interface connection to a JTAG/IEEE 1149.1 TAP. Other low-end versions (ex: 19 channel LVDS) are derived from these two basic models. All BSPIO I/O interfaces have an internal loopback for self test capability.

- Click here to open data sheet

- Click here to view all documents list