## Digital Modules for Boundary Scan Parallel I/O Access

Via Rocca di Papa, 21 –00179 Roma, Italy

Email: <a href="mailto:info@geb-enterprise.com">info@geb-enterprise.com</a> - Web: <a href="mailto:www.geb-enterprise.com">www.geb-enterprise.com</a>

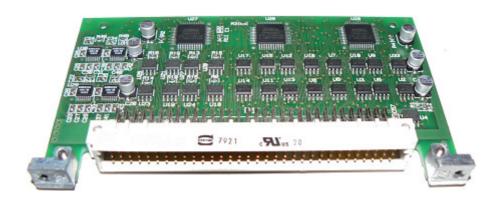

# **Model: BSPIO-STDIF1688**

#### *Features*

- 16 RS485/RS422 I/O channels for interface logic drive and sense

- 8 LVDS I/O channels for interface logic drive and sense

- 8 RS232 Input channels for interface logic sense

- 8 RS232 Output channels for interface logic drive

- High reliability DIN41612 I/O connector

- · Reliable screw lock brackets

- Mechanical dimensions 122mm X 70mm

- 96 bit Boundary-scan Register Length

- · Each segment can be independently bypassed

- Medium-speed 10MHz TCK for high reliability at the best cost/performance ratio

- Each RS485/RS422 or LVDS I/O pin is independently programmable for sense, drive, bi-directional, and tri-state operation

- Fully-compatible JTAG/IEEE 1149.1 Test Access Port (TAP)

- Operating power 3.3V, 5.0V

- Optional LVDS TCK interface can be used in large fixtures to avoid noise and skew problems.

- · Full self test capability using internal loopback.

## **General Description**

The BSPIO-STDIF1688 provides bi-directional parallel-scan access to up to 40 electrical nodes with various distinct interfaces for the driving and sensing of logic values. This module increases the effectiveness of boundary-scan testing, enabling verification of all board connectors and within logic clusters. The BSPIO-STDIF1688 is available in two basic versions, both of them compatible with standard DIN41612 female connectors in a test fixture. One version, the BSPIO-STDIF1688-A1, is primarily intended for test fixtures with few BSPIOs, and contains a standard TTL interface on the TAP's TCK signal. This module facilitates boundary-scan interconnection testing using direct connection to the JTAG/IEEE 1149.1 Test Access Port (TAP).

The other version, the BSPIO-STDIF1688-A2, is intended for test fixtures with many BSPIOs and contains a balanced LVDS interface on the TAP's TCK signal. This module facilitates boundary-scan interconnection testing using a small interface connection to a JTAG/IEEE 1149.1 TAP. Other low-end versions (ex: 16 channel RS422/R485) are derived from these two basic models. All BSPIO I/O interfaces (RS485/RS422, LVDS) have an internal loopback for self test capability, while input only and output only interfaces (RS232) are cross connected via a weak resistor to ensure the self test capability.

## **Functional Description**

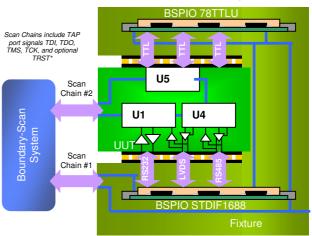

Test and programming application development tools from JTAG Technologies support automatic integration of the BSPIO-STDIF1688 with the target board design by adapter file. This allows the inputs and outputs of the BSPIO-STDIF1688 to be driven and sensed via boundary-scan RS232, RS485, RS422, LVDS interfaces on the target, thereby providing increased scan access. The 40 channels of the BSPIO are capable of operating at a 10 MHz TCK clock rate. The TAP interface available on the DIN41612 connector is the test access port for the module. It can be used to daisy-chain the module to other BSPIO modules (BSPIO-78TTLU, BSPIO-OPTO1212...) or to scan chain on the target board.

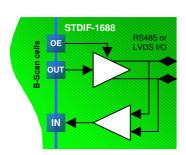

Fig.1 LVDS and RS485/422 I/O cells

Fig.2 Use of the BSPIO-STDIF1688 on the Test Fixture

#### **Specifications**

| Length of ID Register               | 32 bits per segment                               |

|-------------------------------------|---------------------------------------------------|

| Length of Boundary-scan<br>Register | 96 bits per segment,<br>3 segments                |

| Maximum Shift Frequency             | 10MHz                                             |

| Power Consumption                   | typ<60mA, max depending on the target Ioн and IoL |

## **DC Operating Conditions**

| RS485/RS422 I/O | -200mV <vth vtl<200mv<br="">VOD (50Ω)=2V IOZ=1μA</vth> |

|-----------------|--------------------------------------------------------|

| RS232 Input     | VIL<0.8V VIH>2.4V                                      |

| RS232 Output    | -3.7v <vo<+3.7v rl="3KΩ&lt;/td"></vo<+3.7v>            |

| LVDS I/O        | 1 <vos<1.65 vth="" vtl="+/-100mV&lt;/td"></vos<1.65>   |

| <i>TAP</i> (*1) | All VIL<0.8V VIH>2.0V                                  |

| TAP TCK(*2)     | 1 <vos<1.65 vth="" vtl="+/-100mV&lt;/td"></vos<1.65>   |

- (\*1) Not Applicable to TCK version A2

- (\*2) Applicable to TCK version A2

#### Ordering Information

| GEB P.N. (*)            | Description                                             |

|-------------------------|---------------------------------------------------------|

| BSPIO-STDIF1688-A1/A2   | 16 RS485 I/O, 8 LVDS I/O, 8 RS232 Input, 8 RS232 Output |

| BSPIO-STDIF1688-A3/A4   | 8 RS485 I/O, 4 LVDS I/O, 4 RS232 Input, 4 RS232 Output  |

| BSPIO-STDIF1688-A5/A6   | 16 RS485 I/O only                                       |

| BSPIO-STDIF1688-A7/A8   | 16 RS485 I/O, 4 LVDS I/O, 4 RS232 Input, 4 RS232 Output |

| BSPIO-STDIF1688-A9/A10  | 8 LVDS I/O only                                         |

| BSPIO-STDIF1688-A11/A12 | 8 RS485 I/O, 4 RS232 Input, 4 RS232 Output              |

| BSPIO-STDIF1688-A13/A14 | 16 RS485 I/O, 4 RS232 Input, 4 RS232 Output             |

| BSPIO-STDIF1688-A15/A16 | 8 RS485 I/O only                                        |

(\*) Odd-numbered versions (A1,A3...) have LVTTL level on TCK input, Even numbered versions (A2,A4...) have balanced LVDS levels on TCK input

GEB Enterprise s.r.l. reserves the right to make changes in design or specification at any time without notice.

Document Rev. 0.6, Printed 17-10-2008 ©2008 GEB-Enterprise s.r.l.

All brand names or product names mentioned are trademarks or registered trademarks of their respective owners