Timing Analysis Base

Corso introduzione all’analisi di timing per FPGA con TimeQuest in Quartus Prime

VEC107: Analizzatore di timing TimeQuest

Ciclo corsi di programmazione FPGA

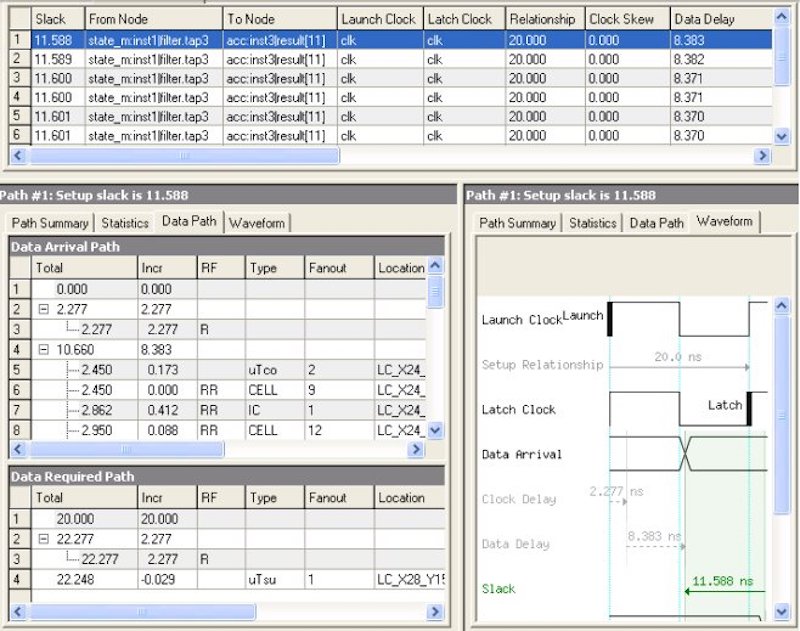

In questo corso FPGA imparerete come indirizzare, costringere e analizzare le temporizzazione di un progetto utilizzando l’analizzatore di temporizzazione TimeQuest presente nel software Quartus® Prime.

Questo includerà la comprensione dei parametri di temporizzazione per circuiti digitali e per FPGA, la scrittura del Synopsys Design Constraint (SDC) file, la generazione dei vari rapporti di temporizzazione mediante analizzatore TimeQuest fino ad applicare la conoscenze acquisite su un progetto FPGA.

Oltre ad imparare i requisiti di base per garantire che il progetto soddisfa i requisiti temporali, vedrete anche come l’analizzatore TimeQuest può rendere facile creare vincoli temporali aiutandovi a soddisfare i requisiti temporali del progetto.

Difatto TimeQuest sarà impiegato sia in modo batch, durante la compilazione quartus per verificare il risultato della sintesi, sia in modalità interattiva per effettuare analisi approfondite dei requisiti applicati al circuito, permettendovi di risolvere le violazioni temporali.

Durata del corso: 2 giorni

Al completamento del corso sarai in grado di:

- Capire le analisi di timing effettuate bel flusso di progetti FPGA con l’analizzatore TimeQuest.

- Applicare vincoli di temporizzazione, sia semplici ma anche complessi, su un progetto FPGA.

- Analizzare la sincronizzazione in un progetto FPGA usando l’analizzatore di temporizzazione TimeQuest

- Scrivere e manipolare un file SDC per l’analisi e controllore (pilotare) la compilazione in Quartus Prime

Competenze richieste:

- Esperienza nell’uso di PC e del sistema operativo windows

- Conoscenza di tecniche di progettazione di logiche digitali

- Completamento del corso “VEC 102, introduzione a Quartus Prime” o una sua buona conoscenza pratica