Quartus Prime Timing Analysis

The course introduces TimeQuest tool and SDC file creation to perform Static Timing Analysis

VEC107E: QUARTUS Prime, Timing Analysis

Fpga training series

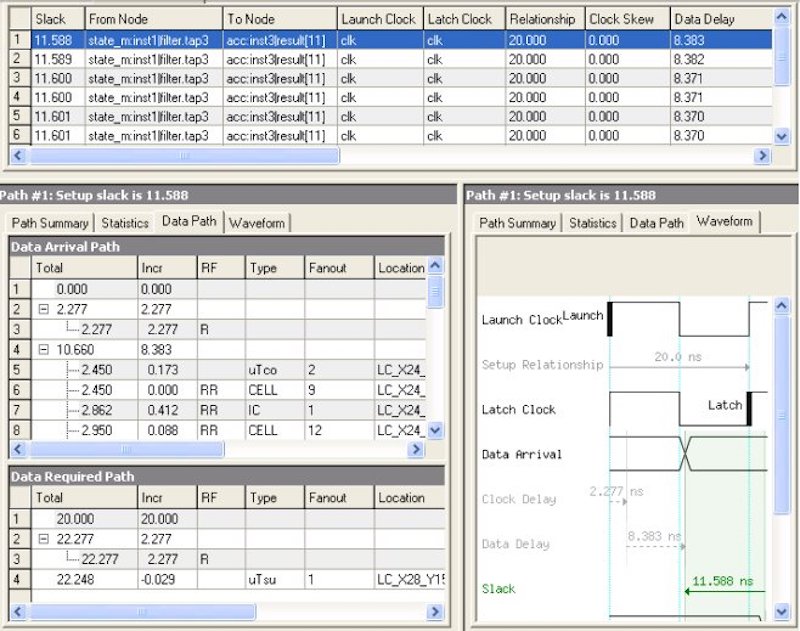

You will learn how to constrain & analyze a design for timing using the TimeQuest timing analyzer in the Quartus® Prime software.

This includes understanding FPGA timing parameters, writing Synopsys Design Constraint (SDC) files, generating various timing reports in the TimeQuest timing analyzer & applying this knowledge to an FPGA design.

Besides learning the basic requirements to ensure that your design meets timing, you will see how the TimeQuest timing analyzer makes it easy to create timing constraints to help you meet those requirements.

Course duration: 2 days

At Course Completion you will be able to:

- Understand the TimeQuest timing analyzer timing analysis design flow

- Apply basic and complex timing constraints to an FPGA design

- Analyze an FPGA design for timing using the TimeQuest timing analyzer

- Write and manipulate SDC files for analysis and controlling the Quartus Prime compilation

Skills Required:

- Experience with PCs and the Windows operating system

- Completion of “VEC102, The Quartus Prime Foundation” course OR a working knowledge of the Quartus Prime software