Quartus Prime Advanced Timing Analysis

Advance Timing Analysis using TimeQuest, mainly how create an SDC file in DDR application

VEC125E: Advanced Timing Analysis with TimeQuest

Fpga training series

In this Fpga Training, using the Quartus® Prime software and building upon your basic understanding of creating Synopsys Design Constraint (SDC) timing constraints, this class will guide you towards understanding, in more depth, timing exceptions.

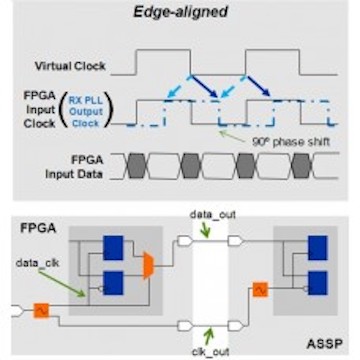

You will learn how to apply timing constraints to more advanced interfaces such as source synchronous single-data rate (SDR), double-data rate (DDR) and LVDS, as well as clock and data feedback systems.

You will discover how to write timing constraints directly into an SDC file rather than using the GUI and then enhance the constraint file using TCL constructs. You will also perform timing analysis through the use of TCL scripts.

Course duration: 2 days

At Course Completion you will be able to:

- Constrain external device with SDR and DDR interfaces

- Write Tcl script files to automate constraining and analysis of FPGA designs

- Apply timing exceptions to real design situations

- Properly constrain and analyze the following design situations: source synchronous interfaces, external feedback designs, and high-speed interfaces containing dedicated SERDES hardware

Prerequisites:

- Completion of “VEC102 The Quartus Prime Foundation” course OR a working knowledge of the Quartus Prime software.

- Completion of “VEC107 The Quartus Prime Timing Analysis (with TimeQuest)” course OR a working knowledge of the TimeQuest timing analyzer and basic SDC commands

- Experience with PCs and the Windows operating system