Progettazione HW PCIE su FPGA

Come progettare e simulare una interfaccia PCIE su FPGA

VEC222: Corso PCIE con FPGA Intel

Ciclo corsi di programmazione FPGA

Vuoi espandere il tuo PC Embedded aggiungendo porte di ingresso e uscita su PCIe? Stai cominciando a lavorare su un progetto che utilizza uno o più interfacce PCI Express®? Hai domande riguardo al link PCIe® su FPGA? Vuoi sapere come costruire il tuo sistema su FPGA in poco tempo? Vuoi sapere come simulare le tue funzioni integrate con una IP PCI express su FPGA Intel®?.

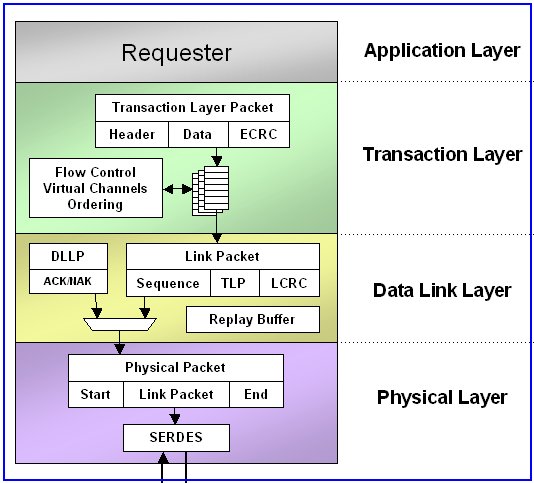

Allora questo corso PCIe dovrebbe interessarti! Inizieremo con una panoramica di alto livello del protocollo PCI Express, a seguire si illustrerà il flusso di progettazione per utilizzo della IP PCI Express hardwired disponibili in Cyclone®V, Arria®V, Arria®10 e Stratix® V, in particolare quando si utilizza lo strumento di progettazione del sistema QSYS.

Vedrai come eseguire la verifica del link PCIe, sia attraverso la simulazione con il simulatore behavioural sia in-system, sulla scheda target. Scoprirai le funzioni dei dispositivi avanzati che danno al tuo progetto su bus PCI Express una marcia in più grazie alla loro grande flessibilità e capacità.

Entro la fine del corso, ti sentirai in grado di “tirare su” agevolmente il tuo collegamento PCIe e avrai la soddisfazione di vederlo funzionare.

Durata del corso: 2 giorni

Al completamento del corso sarai in grado di:

- Definire e configurare le caratteristiche e le funzionalità per la PCIe hardwired IP.

- Costruire una soluzione PCI Express su FPGA utilizzando l’Editor di sistemi QSYS.

- Generare un testbench per simulare la IP PCI Express hardwired e modificarlo per effettuare test personalizzati sulle funzioni personalizzate aggiunte.

- Eseguire il debug del link PCIe utilizzando gli strumenti Intel® (Altera®) e le funzioni del transceiver di supporto al debug

Competenze richieste:

- La conoscenza delle specifiche del protocollo PCI Express è utile, ma non necessaria

- La familiarità con l’architettura transceiver ad alta velocità, in alterativa comune si può visualizzare il corso online “Basics Transceiver”

- La familiarità con flusso di progettazione FPGA/CPLD

- La familiarità con il software di progettazione Quartus Prime

- Una certa familiarità con lo strumento di progettazione QSYS è utile, ma non necessaria