Ottimizzazione OPENCL su FPGA

Corso ottimizzazione del codice OPENCL per la massimizzazione delle prestazioni su FPGA Intel (Altera)

VEC321: Optimizzazione codice OPENCL su FPGA Intel

Ciclo corsi di programmazione FPGA

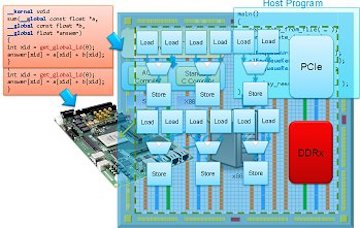

Il corso copre le tecniche di ottimizzazione necessarie per implementare una soluzione OpenCL ad alte prestazioni su FPGA Intel® (Altera®) utilizzando il SDK per OpenCL.

Discuteremo le buone pratiche di codifica, i modi per migliorare l’efficienza d’elaborazione dei dati, l’efficienza di accesso alla memoria, e l’ottimizzazioni delle interazione sul lato host.

Ci concentreremo anche sulle caratteristiche specifiche del SDK Intel® per OpenCL che possono migliorare significativamente le prestazioni di OpenCL targettando il codice su FPGA rispetto ad altre piattaforme.

Durata del corso: 2 giorni

Al completamento del corso sarai in grado di:

- Utilizzare le buone pratiche di progettazione e di codifica per implementare un sistema OpenCL ad alte prestazioni su FPGA

- Applicare diversi metodi per migliorare l’efficienza di elaborazione dei dati del kernel OpenCL

- Migliorare l’efficienza di accesso alla memoria del sistema

- Ottimizzare le operazioni lato host

- Comprendere le caratteristiche specifiche delle FPGA Intel® che permetteranno di migliorare in modo significativo le prestazioni di una soluzione OpenCL

Prerequisiti e competenze necessarie:

- Completamento del corso VEC311, Calcolo Parallelo con OpenCL o una buona comprensione degli standard OpenCL