Introduzione al VHDL

Corso VHDL per FPGA, basi del liguaggio sintetizzabile e simulazioni VHDL

VEC100: Corso VHDL Base

Ciclo corsi di programmazione FPGA

Questo “corso VHDL base” è un’introduzione generale al linguaggio VHDL e al suo utilizzo nella progettazione di logiche programmabile su FPGA o PLD. L’enfasi è posto sui costrutti di sintesi di VHDL (comunemente detto VHDL sintetizzabile).

Potrai acquisire una conoscenza di base di VHDL per poter iniziare a creare i files di progetto di una FPGA. Nelle sessioni pratiche di laboratorio, questa tua nuova conoscenza verrà messa alla prova scrivendo progetti semplici ma pratici; questo ti permetterà, con il supporto dell’istruttore, di risolvere i dubbi che logicamente sorgono alla prima applicazione della nuova metodologia di progetto.

Potrai verificare i tuoi progetti compilando nell’ambiente software Quartus® Prime e simulando nell’ambiente di simulazione ModelSim®-Intel®.

Durata del corso: 2 giorni

Al completamento del corso sarai in grado di:

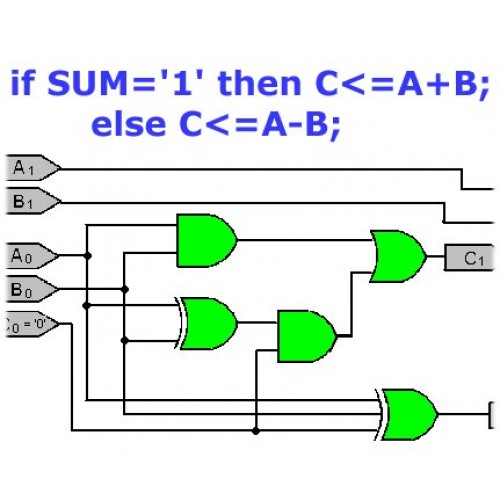

- Implementare i costrutti VHDL di base

- Usare le design units VHDL: Entity, architecture, configuration, package

- Creare modelli comportamentali e strutturali

- Usare degli operatori aritmetici

- Scrivere macchine a stati

- Incorporare blocchi strutturali

Competenze richieste:

- Il background di progettazione logica digitale è indispensabile

- Una conoscenza della simulazione non è necessaria ma utile

- Una conoscenza di un linguaggio di programmazione (ad esempio il linguaggio “C”) non è necessaria ma utile

- Non è necessaria alcuna conoscenza del VHDL o del software Quartus Prime