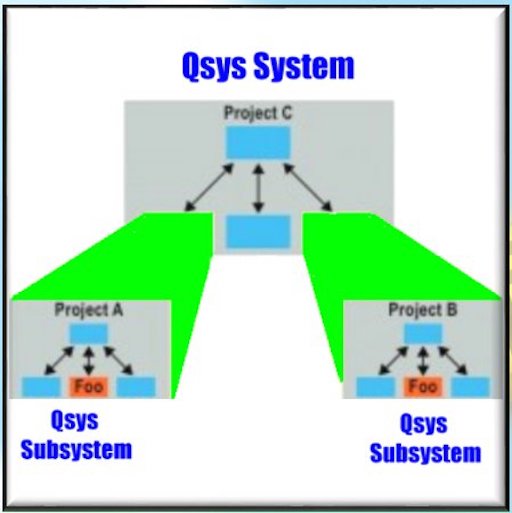

Introduzione a QSYS

Corso Fpga su come creare un sistema o una periferica senza scrivere codice VHDL

VEC110: Corso QSYS, Editor di sistemi gerarchici

Ciclo corsi di programmazione FPGA

Questo corso di progettazione FPGA vi insegnerà come costruire rapidamente progetti per FPGA Intel® utilizzando lo strumento di editing e integrazione di sistema QSYS sviluppato dall’Intel® (ex Altera).

Tu diventerai più efficente utilizzando QSYS ed espanderai la tua conoscenza del software di progettazione FPGA Quartus® Prime.

Imparerai come utilizzare rapidamente le IP standard presenti in libreria e ad integrarvi la tua logica personalizzata atta a realizzare i TUO sistema per la TUA specifica applicazione.

Visto che QSYS rende il riutilizzo dei progetti facile attraverso interfacce standard, esamineremo insieme le interfacce:

- Intel® Avalon-MM, memory mapped, master e slave.

- Intel® Avalon-ST, Streaming, Source e Sink.

Saranno anche introdotte le interfacce standard AMBA™ e AXI®, usate dal processore ARM®.

Il corso comprende molte esercitazione pratiche significative, dove guadagnerai confidenza con l’uso dello strumento, sia per la progettazione di sistema sia dei sui componenti personalizzati, descritti mediante codice HDL (Verilog, VHDL) ma anche mediante schema elettrico tradizionale

Durata del corso: 2 giorni

Al completamento del corso sarai in grado di:

- Costruire sistemi digitali nello strumento QSYS

- Integrare i file generati da QSYS nel flusso di progettazione Quartus Prime

- Creare dei componenti personalizzati, con interfacce sia Avalon-MM sia Avalon-ST, e di integrarli nel tuo sistema

Competenze richieste:

- Conoscenza della progettazione di logica digitale

- Corso FPGA, VEC102 Introduzione a Quartus Prime o la conoscenza pratica del suo funzionamento

- Nozioni della metodologia di codifica HDL (utile ma non obbligatorio)