Introduction to VHDL

The class explains VHDL language for synthesis

VEC100E: Introduction to VHDL training

Fpga programming courses series

This fpga course is an introduction to the VHDL language dedicated to the Electronics Designers that want to increase their productivity in the fpga and pld development. The basic VHDL training covers many of the constructs used in the synthesis and also someone used during simulations.

Before the training end, you will gain the basic understanding of VHDL method so that you can start your own designs, using the behavioral approach to descrive the functionality and structural approach to join all in large designs.

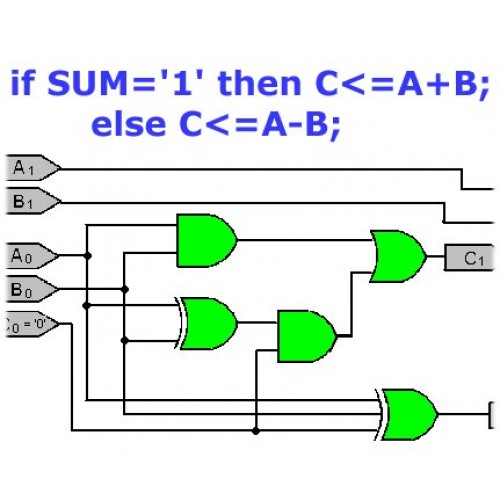

You will start learn the efficient coding techniques for writing synthesizable VHDL and getting practice in uses of variables and signals, concurrent and sequential statements, description with implicit and explicit processes.

Will be shown simple rules to avoid encoding errors that can invalidate the simulation.

In the hands-on laboratory session, you will get to practical knowledge by writing simple but practical projects. You’ll check your designs by compiling in the Quartus Prime software and will begin to learn simulation methods in the Intel® ModelSim® tool.

Course duration: 2 days

At Course Completion you will be able to:

- Implement basic VHDL constructs

- Use VHDL design units: entity, architecture, configuration and package

- Create behavioral and structural models in VHDL

- Using arithmetic operators

- Writing state machines

- Incorporate structural blocks

Skills Required:

- Background in digital logic design

- Knowledge of simulation is a plus

- Prior knowledge of a programming language (e.g., “C” language) is a plus

- No prior knowledge of VHDL or Quartus Prime software is needed