Designing with DSP Builder

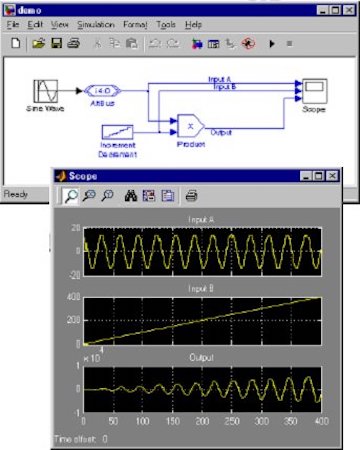

How You Use MATLAB and SIMULINK to generate VHDL synthesizable code using the Intel (Altera) DSP Builder

VEC220E: Designing with DSP Builder Advanced Blockset

Fpga programming courses series

Learn the timing-driven Simulink® design flow to implement high-speed DSP designs. This course focuses on implementing DSP algorithms using the advanced blockset capability of DSP Builder—an interface between Quartus® Prime software & MATLAB® and Simulink tools from The MathWorks®. You’ll analyze & design your DSP algorithm using the DSP Builder advanced blockset in MATLAB & Simulink.

You’ll explore architecture & performance tradeoffs with system-level constraints. Also you’ll verify functionality & performance of generated hardware in the Quartus Prime software. Finally, you’ll speed design time by incorporating ready made ModelIP cores in your design.

Course duration: 3 days

At Course Completion you will be able to:

- Implement DSP algorithms using Intel® DSP Builder Advanced Blockset

- Incorporate ModelIP and ModelPrim cores in a design

- Explore design architecture and performance tradeoffs using system level constraints

- Incorporate a DSP Builder Advanced Blockset model into a Qsys subsystem

- Verify the hardware performance and implementation in Quartus Prime software

Skills Required:

- Familiarity with DSP fundamentals and design

- Familiarity with MATLAB® and Simulink® from MathWorks® is helpful, but not necessary

- Familiarity with digital modem design is helpful, but not necessary